Product Description:

1. Display interface bridge chip for converting LVDS interface signals to MIPI DSI or eDP signals.

2. Supports maximum resolutions of 1366×768, 1280×800, and 800×1280.

3. Supports single-channel LVDS input, including LVDS data lane swapping and P/N polarity inversion.

4. Compliant with MIPI DSI Specification V1.1 and D-PHY Specification V1.1.

5. MIPI DSI mode supports both Command mode and Video mode transmission.

6. MIPI DSI supports 1/2/4 data lanes with a maximum speed of 1Gbps per lane.

7. Compliant with eDP Specification V1.3.

8. eDP supports 1-lane and 2-lane configurations, with speeds of 1.62Gbps and 2.7Gbps.

9. Integrated 24MHz crystal oscillator circuit and supports external 24MHz clock input.

10. Default I2C device address: 0xC8, supporting standard mode (100kbps).

11. Supports 13 GPIOs, with 10 GPIOs multiplexed with MIPI DSI signals.

12. Package: QFN48.

13. Dimensions: 6mm × 6mm.

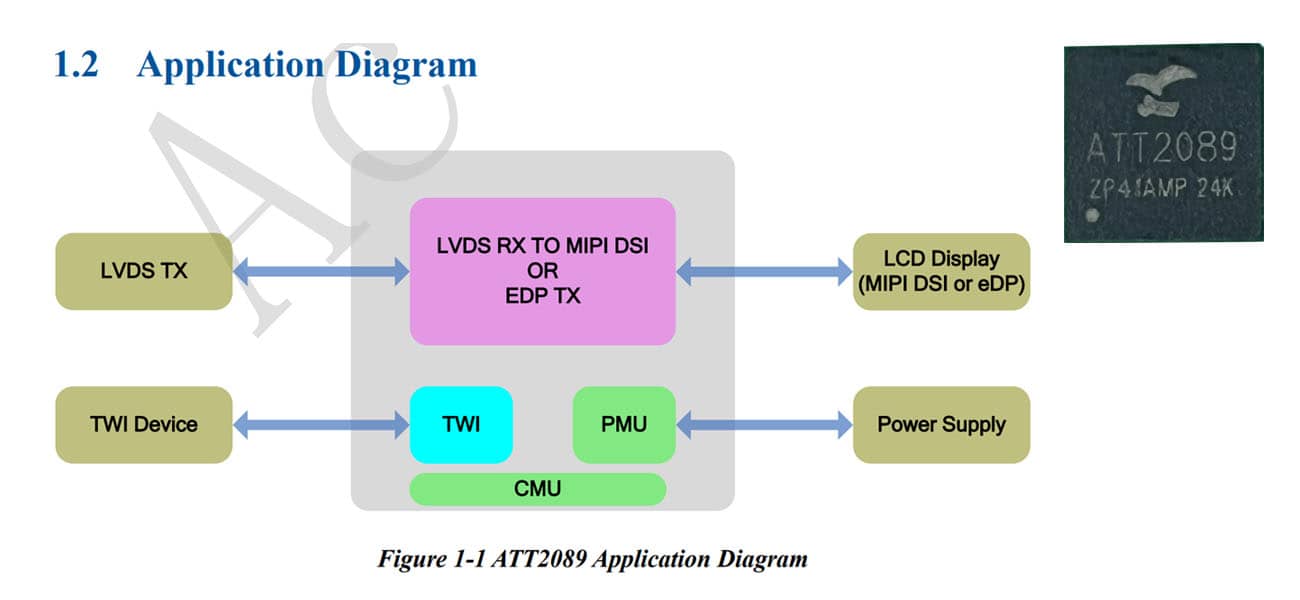

Products Application:

1. Display interface signal conversion board.

2. Front-end signal processing for MIPI display panels.

3. Supports driving MIPI panels with LVDS output.

Product examples:

|

MIPI panel for digital photoframe |

|

MIPI panel for video player |

|

MIPI panel for HMI display |